Na confecção de uma Placa de Circuito Impresso, ou da sigla PCB em inglês, existem boas práticas que devem ser sempre aplicadas. Vamos, aqui, listar 10 dessas práticas que devem estar sempre na mente de todo o engenheiro para o desenvolvimento de produtos eletrônicos.

Essas práticas visam minimizar problemas com EMC, EMI, Loops de Terra, acoplamentos, entre outros problemas comuns em PCB. Já tivemos um artigo no site sobre Loops de PCI e outro sobre EMC, além de um sobre PCB Multicamada, todos escritos pelo Thiago Lima. Vale a pena conferir.

Confira também o Webinar sobre Projeto de PCB, com Edson Camilo, no Embarcados.

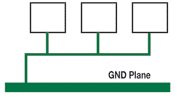

1. Planos de Terra de uma PCB

Um Plano de Terra (Ground Plane) de baixa indutância é fundamental para minimizar problemas de EMC. Maximizar as áreas de terra de uma PCB reduz a indutância de terra em um sistema, que por sua vez reduz as emissões eletromagnéticas e o Crosstalk.

Conectando todos os terras individuais e, em seguida, conectá-los ao plano de terra, não é aconselhável, pois aumenta o tamanho da malha de corrente. Os sinais podem acabar se acoplando ao terra de diferentes maneiras. Se os componentes estiverem ligados de maneira aleatória ao terra do sistema, teremos uma PCB de baixa qualidade. Esse problema de layout gera alta indutância e problemas sérios de EMC.

A forma como um sinal de volta à terra do sistema é muito importante, pois quando um sinal toma um caminho mais longo, ele cria um loop de terra, que forma uma antena e irradia energia. Assim, toda a trilha que flui corrente de volta para a fonte deve seguir o caminho mais curto possível, e deve ir diretamente para o plano de terra.

Uma abordagem de design recomendada é ter um plano inteiro de terra, pois isso proporciona menor impedância para as correntes de retorno.

No entanto, um plano de terra requer uma camada PCB dedicada, que pode não ser possível para PCBs de duas camadas. Neste caso, os designers devem usar grids de terra, como abaixo. A indutância de terra neste caso dependerá do espaçamento entre as redes.

2. Agrupamento e Placement na PCB

Para um projeto livre de EMC, componentes no PCB devem ser agrupados de acordo com sua funcionalidade, tais como, seções analógicas, seções digitais, fonte de alimentação, circuitos de baixa velocidade, circuitos de alta velocidade, e assim por diante. As trilhas para cada grupo devem permanecer em sua área designada.

Além da separação em seções, é recomendado a separação das alimentações. Deve-se fazer planos por funções, fazendo a ligação entre os planos de terra em pontos definidos. Isso significa que, mesmo que eletricamente conectados, tratam-se de planos de terra diferentes.

Para um sinal fluir de um subsistema para outro, um filtro deve ser utilizado nos limites entre os sistemas.

3. Camadas da PCB

Arranjo adequado das camadas é vital do ponto de vista do EMC. Se forem utilizadas mais do que duas camadas, uma camada completa deve ser utilizada como um plano de terra. No caso de uma placa de quatro camadas, a camada por baixo do plano de terra deve ser utilizada como um plano de VCC.

Deve-se tomar cuidado para que o plano de terra esteja sempre entre as trilhas de sinal de alta frequência e o plano de VCC. Se planos de alimentação separados não puderem ser usados, então a trilha de terra deve correr em paralelo com a de VCC para manter a alimentação sem ruídos.

4. Circuitos Digitais

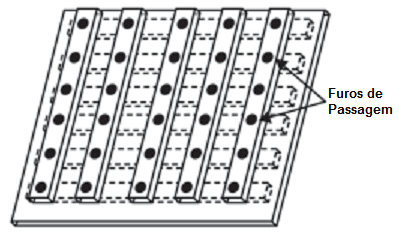

Ao lidar com circuitos digitais, deve ser dada atenção extra para os sinais de clock e outros sinais de alta velocidade. Trilhas de ligação desses sinais devem ser as mais curtas possíveis e estarem ao lado do plano de terra para manter a radiação e crosstalk sob controle. Com estes sinais, deve-se evitar o uso de furos de passagens, ou trilhas de roteamento na borda PCB, ou mesmo próximos conectores. Esses sinais também devem ser mantidos fora do plano de alimentação, uma vez que pode induzir ruído no plano de energia também.

Quando rotear trilhas de um cristal ou oscilador, nenhuma outra trilha deverá ser roteada paralela a esta, ou mesmo abaixo do cristal, além do terra. O cristal precisa estar muito próximo dos componentes que utilizarão seu sinal. Também é importante notar que a corrente de retorno sempre segue o caminho menos reativo. Portanto, trilhas de terra que transportam corrente de retorno deve ser mantido perto destes sinais.

Trilhas que transportam sinais diferenciais devem ser roteadas próximas destes para utilizar de forma mais eficaz a vantagem de cancelamento campo magnético.

5. Casamento de Impedância

Trilhas que transportam sinais de alta frequência, como o clock, de uma fonte qualquer para um dispositivo, devem ter terminações correspondentes. Isso porque, sempre que há uma diferença de impedância, uma parte do sinal é refletida.

Se os cuidados adequados não são tomados para lidar com este sinal refletido, uma grande quantidade de energia será irradiada. Reflexões estão intimamente relacionadas com a teoria de antenas, mas diferente o suficiente para justificar a sua própria discussão. Quando uma trilha de uma PCB faz um ângulo de 90º, pode ocorrer uma reflexão.

Em um ângulo reto, a largura da trilha é aumentada para 1.414 vezes a sua largura original. Isso atrapalha as características da linha de transmissão, especialmente a capacitância distribuída e a indutância, resultando na reflexão. No entanto não é possível fazer uma PCB apenas com linhas retas. A maioria dos sistemas CAD e EDA possuem funções automáticas para dar algum efeito de arredondamento no traçado.

6. Circuitos Analógicos

Trilhas que transportam sinais analógicos devem ser mantidas longe de sinais de alta velocidade ou de chaveamento, e devem sempre estar protegidas com planos de terra. Filtro passa-baixa deve sempre ser usado para se livrar de ruídos de alta frequência que se acoplam pelas trilhas analógicas. Além disso, é importante não compartilhar o plano de terra com circuitos digitais, como dissemos anteriormente.

7. Capacitor de Desacoplamento

Qualquer ruído na fonte de alimentação tende a alterar o funcionamento de um dispositivo em operação. Geralmente, o ruído acoplado na fonte de alimentação é de uma alta frequência. Por isso, capacitores de bypass ou capacitores de desacoplamento são necessários para filtrar este ruído.

Um capacitor de desacoplamento fornece um caminho de baixa impedância para sinais de alta frequência no plano de VCC para o terra. O caminho seguido pela corrente à medida que é conduzida em direção ao terra forma um loop de terra. Este caminho deve ser o menor possível, seguindo pelos capacitores de desacoplamento. Um loop de terra grande aumenta a radiação e pode agir como uma fonte potencial de falha por EMC.

A proximidade do capacitor com o circuito que deseja-se proteger é fundamental, pois longas distâncias de trilhas significam indutâncias indesejadas em série. Além disso, a reatância de um capacitor ideal se aproxima de zero com o aumento da frequência. Infelizmente, não existe capacitor ideal. Além disso, o chumbo e o encapsulamento adicionam indutância. Capacitores com baixo ESL (indutância em série equivalente) devem ser usados para melhorar o efeito de desacoplamento.

Tabela 1: Frequência máxima dos capacitores.

| Tipo do Capacitor | Frequência Máxima |

| Eletrolítico de Alumínio | 100KHz |

| Eletrolítico de Tântalo | 1MHz |

| Mica | 500MHz |

| Cerâmico | 1GHz |

Tipicamente adota-se a seguinte prática. Capacitores de 100nF cerâmico próximos a cada semicondutor do dispositivo, ligados a cada ponto de entrada de alimentação. Se sua situação é um circuito de alta potência, ou sinais de alta frequência, é importante pensar em outros valores e posições com cuidado.

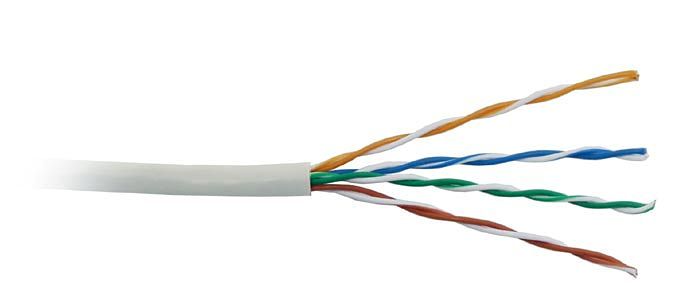

8. Fios e Cabos

A maioria dos problemas relacionados com EMC são causadas por cabos que transportam sinais digitais que atuam efetivamente como uma antena eficiente. Idealmente, a corrente que entra um cabo sai do outro lado, mas na realidade as coisas são diferentes por causa da indutância e capacitância parasitas que emitem radiação.

Usar um cabo de par trançado ajuda a manter o acoplamento a um nível baixo, minimizando os campos magnéticos induzidos. Quando um flat-cable é usado, devem ser fornecidos vários caminhos de retorno à terra. Para sinais de alta frequência, cabos blindados devem ser utilizados, onde a blindagem está ligada à terra.

9. Crosstalk

O crosstalk pode existir entre duas quaisquer trilhas sobre um PCB e acontece por conta da indutância mútua e capacitância mútua. É dependente da distância entre as duas trilhas, a frequência do sinal, e a impedância das trilhas.

Em sistemas digitais, crosstalk causada por indutância mútua é tipicamente maior do que o crosstalk causada por capacitância mútua. Essa indutância mútua pode ser reduzida, aumentando o espaçamento entre os dois traços ou através da redução da distância entre o plano de terra.

10. Blindagem

Blindagem não é uma solução elétrica, mas uma abordagem mecânica para reduzir EMC. Caixas metálicas, feitos de materiais condutores e/ou magnéticos, são usados para evitar que a EMI irradie para fora do sistema.

A blindagem pode ser utilizada para cobrir todo o sistema ou uma parte do mesmo, dependendo dos requisitos. Funciona como um recipiente fechado condutor ligado ao terra, que reduz eficazmente a EMI porque absorve e reflete parte da sua radiação.

Parabéns pelo conteúdo!

Excelente artigo!

Favoritado! Excelente artigo.

Separar planos de terra em uma PCB (como dito no item 6), poderá levar um projeto a ruína, principalmente se ele precisar ser aprovado em testes de conformidades em EMI.

A preocupação com trilhas com ângulos retos, caso não sejam usadas frequências de 10GHz e/ou existam trilhas largas (100 mil) na faixa de microondas, não passa de mito.

Abs

Olá, sou novo no site e gostaria de saber se as páginas oferecem opção de impressão e porte para PDF. Desde já grato.

Control + P

Existe algum diâmetro padrão para os furos de passagem da [Figura 3] e também uma medida padrão para distância entre furos? Como deve ser calculado isso?

Excelente matéria de reflexão, análise e consulta técnica!

Sobre o plano de terra, tenho uma dúvida. Qual diferença para uso do plano de terra sólido para o plano de terra em malha ou harched (malha).

Concordo com o colega, ótimo artigo, obrigado pelas dicas e se possível, siga nesse assunto.

Excelente artigo. Espero que tenha mais.

Parabéns pelo Artigo Francesco! Muito legal essa compilação de dicas, deve ter sido extremamente difícil escolher só 10! hahah